# MP3120 1.2A, 1.1MHz Synchronous Boost Converter with Output Disconnect

The Future of Analog IC Technology

# DESCRIPTION

The MP3120 is a high efficiency synchronous, current mode step-up converter. The device can boost a single cell or two cells AA battery up to 5V.

The MP3120 can start up from an input voltage as low as 0.8V and provide in-rush current limiting as well as output short circuit protection. The integrated P-Channel synchronous rectified switch provides improved efficiency and eliminates the need of an external schottky diode. The P-MOS will disconnect the output from the input when EN is low. This output disconnect feature allows the output to be completely discharged, thus allowing the part to draw less than 1uA off current in shutdown mode.

The 1.1MHz switching frequency allows for smaller external components; the internal compensation and soft start minimize the external component count, all helps to produce a compact solution for a wide range of load current.

The MP3120 features an integrated power MOSFET that supports up to 5V output and a typical 1.2A switch current.

The device also can maintain the output voltage regulated even when the input voltage is above the output voltage.

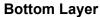

| The | MP3120 | is | offered | in | а | 6-lead | ThinSOT23 |

|-----|--------|----|---------|----|---|--------|-----------|

| pac | kage   |    |         |    |   |        |           |

# FEATURES

- Up to 96% Efficiency

- True Output Disconnect from Input

- Inrush Current Limiting and Internal Soft-Start

- 0.8V Low Voltage Start-Up

- Internal Synchronous Rectifier

- Current Mode Control with Internal Compensation

- Short-Circuit Protection

- 1.1MHz Fixed Frequency Switching

- 0.8V to 5V Input Range

- 2.5V to 5V Output Range

- Tiny External Components

- Small 6-lead ThinSOT Package

## APPLICATION

- Single-cell, Two-cell and Three-cell Alkaline, NiCd or NiMH or single-cell Li Battery Consumer Products

- MP3 Players

- Wireless Mouse

- Audio Recorders

"Monolithic Power Systems", "MPS", and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

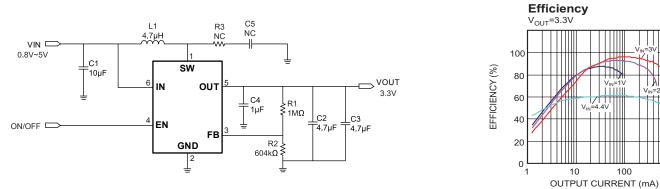

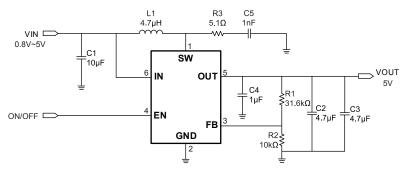

## **TYPICAL APPLICATION**

93 Www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2011 MPS. All Rights Reserved. 1000

## **ORDERING INFORMATION**

| Part Number* | Package  | Top Marking | Free Air Temperature (T <sub>A</sub> ) |  |  |

|--------------|----------|-------------|----------------------------------------|--|--|

| MP3120DJ     | TSOT23-6 | 9A          | -40°C to + 85°C                        |  |  |

\* For Tape & Reel, add suffix –Z (eg. MP3120DJ–Z).

For RoHS compliant packaging, add suffix -LF (eg. MP3120DJ-LF-Z)

# PACKAGE REFERENCE

# ABSOLUTE MAXIMUM RATINGS (1)

| V <sub>IN</sub> Voltage              | 0.3V to 5V                             |

|--------------------------------------|----------------------------------------|

| SW Voltage                           |                                        |

| EN, FB Voltage                       | 0.3V to 6V                             |

| V <sub>OUT</sub> Voltage             | 0.3V to 6V                             |

| Continuous Power Dissipation         | (T <sub>A</sub> =+25°C) <sup>(2)</sup> |

|                                      | 0.45W                                  |

| Operation temperature T <sub>A</sub> | 40°C to + 85°C                         |

| Junction temperature T <sub>J</sub>  | -40°C to + 125°C                       |

| Lead temperature                     | 250°C                                  |

| Storage temperature                  | -65°C to + 150°C                       |

|                                      | (2)                                    |

## Recommended Operating Conditions <sup>(3)</sup>

Supply Voltage V<sub>IN</sub>.....0.8V to 5V Operating Junct. Temp (T<sub>J</sub>)..... $-40^{\circ}$ C to  $+125^{\circ}$ C

Thermal Resistance  $^{(4)}$   $\theta_{JA}$   $\theta_{JC}$

## TSOT23-6......220.....110...°C /W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) = ( $T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  =1.8V,  $V_{OUT}$ =5V.  $T_A$ =25°C.  $V_{EN}$ =5V, unless otherwise noted.

| Parameters                               | Symbol                  | Condition                                            | Min  | Тур  | Max  | Units |

|------------------------------------------|-------------------------|------------------------------------------------------|------|------|------|-------|

| Minimum Startup Voltage                  | V <sub>ST</sub>         | V <sub>OUT</sub> =0V                                 |      | 0.7  | 0.85 | V     |

| Minimum Operating Voltage <sup>(5)</sup> | V <sub>IN</sub>         | V <sub>EN</sub> =V <sub>IN</sub>                     |      | 0.3  | 0.52 | V     |

| Feedback Voltage                         | $V_{FB}$                |                                                      | 1.17 | 1.21 | 1.25 | V     |

| Feedback Input Current                   | I <sub>FB</sub>         | V <sub>FB</sub> =1.2V                                |      | 0.9  | 100  | nA    |

| Quiescent Current (Active)               | Ι <sub>Q</sub>          | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      | 470  | 600  | μΑ    |

| Quiescent Current(Shutdown)              | I <sub>Q_SHDN</sub>     | Measured on V <sub>IN</sub> ,<br>VOUT=0V             |      | 0.1  | 1    | uA    |

| NMOS Switch On Resistance                | R <sub>N-MOS(on)</sub>  |                                                      |      | 290  |      | mΩ    |

| PMOS Switch On Resistance                | R <sub>P-MOS(on)</sub>  |                                                      |      | 530  |      | mΩ    |

| NMOS Switch Leakage                      |                         | V <sub>SW</sub> =V <sub>IN</sub> =6V                 |      | 0.1  | 5    | uA    |

| PMOS Switch Leakage                      |                         | V <sub>SW</sub> =0V, V <sub>OUT</sub> =6V            |      | 0.1  | 1    | uA    |

| NMOS Current Limit                       | I <sub>LIM(close)</sub> |                                                      |      | 1.2  |      | Α     |

| PMOS Current Limit                       | I <sub>LIM(open)</sub>  |                                                      |      | 1.2  |      | Α     |

| Maximum Duty Cycle                       | D <sub>MAX</sub>        | V <sub>FB</sub> =1.1V                                | 85   | 91.5 | 98   | %     |

| Minimum On Time                          | T <sub>(on)min</sub>    |                                                      |      | 120  |      | ns    |

| Switching Frequency                      | f <sub>SW</sub>         |                                                      | 865  | 1050 | 1155 | kHz   |

| EN Input High                            | $V_{EN}$                |                                                      | 0.7  |      |      | V     |

| EN Input Low                             | $V_{EN}$                |                                                      |      |      | 0.15 | V     |

| Soft-Start Time                          | Τs                      |                                                      | 0.7  | 1.6  | 2.6  | ms    |

Notes:

5) Minimum V<sub>IN</sub> operation after start-up is limited by the battery's ability to provide the necessary power as it enters a deeply discharged state.

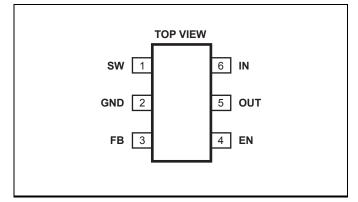

## **PIN FUNCTIONS**

| Pin # | Name | Pin Function                                                                                                                                                                                                                                |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | SW   | Output switch node. SW is the drain of the internal N-Channel and P-Channel MOSFETs. Connect the inductor to SW to complete the step-up converter.                                                                                          |

| 2     | GND  | Ground                                                                                                                                                                                                                                      |

| 3     | FB   | Feedback input to the error amplifier. Connect resistor divider to this pin. The output voltage can be adjusted from 2.5V to 5V by: $V_{OUT} = 1.2V^* [1 + (R1/R2)]$                                                                        |

| 4     | EN   | Regulator on/off control input. A logic high input ( $V_{EN}$ >0.5V) turns on the regulator. A logic low input ( $V_{EN}$ <0.17V) turns off the regulator.                                                                                  |

| 5     | OUT  | Output node. OUT is the source of the P-Channel MOSFET. Connect the OUT pin to the output of the converter. The output capacitor must be as close as possible to the IC and provide shortest PCB trace loop between IC OUT pin and GND pin. |

| 6     | IN   | Input node                                                                                                                                                                                                                                  |

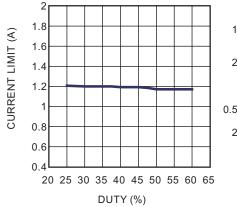

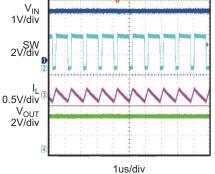

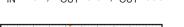

#### TYPICAL PERFORMANCE CHARACTERISTICS C1=10µF, C2=C3=4.7µF, L1=4.7µH, T<sub>A</sub>=25°C, unless otherwise noted. Efficiency vs. Output Current Efficiency vs. Output Current Load Regulation vs. V<sub>OUT</sub>=5V V<sub>OUT</sub>=3.3V **Output Current** V<sub>OUT</sub>=3.3V 0.2 ||||| V<sub>IN</sub>⁼ **REGULATION (%)** 0.0 100 100 -0.2 EFFICIENCY(%) EFFICIENCY(%) 80 Ш 80 -0.4 60 -0.6 60 Λ -0.8 40 LOAD 40 -1.0 20 20 -1.2 0 -1.4 0 10 100 1000 1 10 100 1000 100 1000 10 1 1 OUTPUT CURRENT(mA) OUTPUT CURRENT(mA) OUTPUT CURRENT(mA) **Current Limit Steady Waveform Steady Waveform** V<sub>IN</sub>=2.5V, V<sub>OUT</sub>=3.3V, I<sub>OUT</sub>=0mA V<sub>IN</sub>=2.5V, V<sub>OUT</sub>=3.3V, I<sub>OUT</sub>=500mA

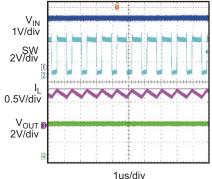

**Steady Waveform** VIN=4.4V, VOUT=3.3V, IOUT=0mA

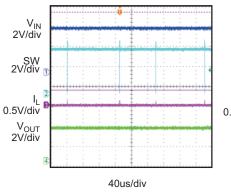

**Steady Waveform** V<sub>IN</sub>=4.4V, V<sub>OUT</sub>=3.3V, I<sub>OUT</sub>=500mA

MP3120 Rev. 0.93 9/20/2011

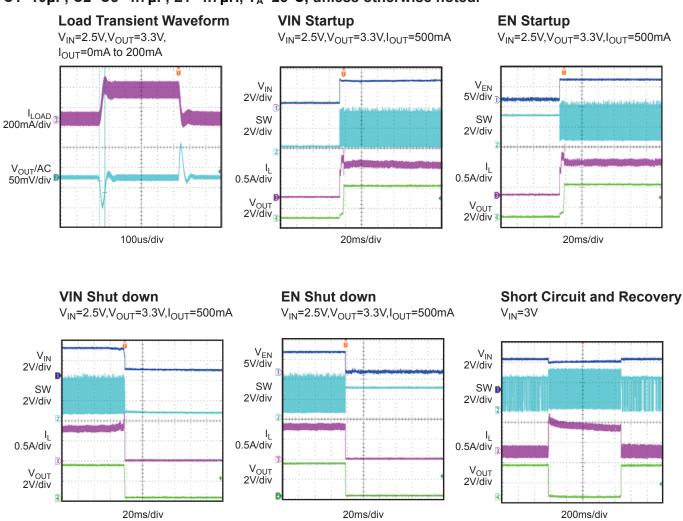

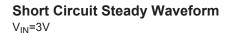

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

C1=10µF, C2=C3=4.7µF, L1=4.7µH, T<sub>A</sub>=25°C, unless otherwise noted.

MP3120 Rev. 0.93 9/20/2011 MPS P

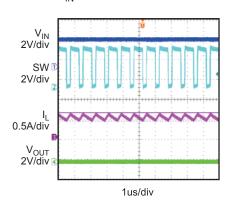

## **BLOCK DIAGRAM**

## **OPERATION**

The MP3120 is a 1.1MHz synchronous boost converter housed in a TSOT-23 package, it is able to operate from an input voltage as low as 0.8V. The device features fixed frequency, current mode PWM control, true output disconnection, and short circuit protection. Detailed descriptions of the different operating modes can be seen as follow. Operation can be best understood by referring to the Function Block Diagram.

### Low Voltage Start-Up

The MP3120 includes an independent start-up oscillator designed to start up at input voltage of 0.8V.In this mode, the IC operates with about 65% duty cycle and open-loop. Once the output voltage exceeds 2.3V, the start-up circuit is disabled and normal close-loop PWM operation is initiated. In normal mode, the MP3120 is powered by  $V_{OUT}$  instead of  $V_{IN}$ . This feature allows the battery voltage to drop even below 0.8V without affecting the circuit operation. The only limiting factor in the application becomes the

ability of the battery to supply sufficient energy to the output. Soft-start and inrush current limiting are provided during start-up as well as normal mode operation.

### **Device Enable**

The device starts to work when EN is higher than 0.5V. And it shuts down when EN is lower than 0.17V. In shutdown mode, the regulator stops switching, all internal control circuit is off, and the load is disconnected from the input.

### **Error Amp**

The error amplifier is an internally compensated transconductance type amplifier. The internal 1.2V reference voltage is compared with the voltage at the FB pin to generate an error signal at the output of the error amplifier.

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2011 MPS. All Rights Reserved.

MP3120 Rev. 0.93 9/20/2011 MF

## **Current Sensing**

Lossless current sensor converts the N-MOS switch current signal to a voltage signal and it is summed with the internal slope compensation.

The summed signal is compared with the error amplifier output to provide a series of PWM signal. The current limit threshold is about 1.2A which is independent of input and output voltage. The switch current signal is blanked for 60ns to enhance noise rejection.

## Synchronous Rectifier

The P-MOS synchronous rectifier is only enabled when  $V_{OUT} > (V_{IN} + 0.1V)$  and the FB pin is above 800mV.

## **Thermal Shutdown**

An internal temperature monitor will start to reduce the peak current limit if the die temperature exceeds 125°C. lf the die temperature continues to rise and reaches to 160°C, the part will thermally shutdown, all switches will be turned off. The part will be enabled again when the die temperature drops by about 20°C.

### **Output Disconnect and Inrush Current** Limiting

The MP3120 is designed to allow true output disconnect by eliminating body diode conduction of the internal PMOS rectifier. This allows VOUT to go to zero volts during shutdown, and drawing zero current from the input source. It also allows for inrush current limiting during start-up, minimizing surge currents from the input. Note that to obtain the advantage of output disconnect, there must be no external schottky diode connected between the SW pin and OUT pin.

Board layout is extremely critical to minimize voltage spike on SW pin caused by stray inductance. Keep the output filter capacitors as close as possible to the OUT pin and use very low ESR/ESL ceramic capacitors tied to a good ground plane.

### Short Circuit Protection

Unlike most boost converters, the MP3120 allows the output to be short circuit due to the output disconnect feature. The device incorporates internal features such as current limit feedback, thermal regulation and thermal shutdown to prevent the chip from burning out caused by excessive overload or short circuit. In the event of a short circuit, the current limit reduces to a smaller value. The thermal protection circuit also functions in addition to the current limit in case of the device temperature rise up to above 125°C.

## V<sub>OUT</sub>< V<sub>IN</sub> Operation

The MP3120 maintains the output voltage to be regulated even if the input voltage is above the output voltage. In this mode the P-MOS no longer acts as a low impedance switch, there will be more power dissipation within the IC. This will cause a sharp drop in the efficiency. The maximum output current should be limited in order to maintain an acceptable junction temperature.

## **APPLICATION INFORMATION**

#### Setting the Output Voltage

The external voltage divider from OUT to GND programs the output voltage via FB from 2.5V to 5V according to the formula:

$$V_{OUT} = 1.2V \times \left(1 + \frac{R1}{R2}\right)$$

#### Setting the Inductor

The inductor with 1.6A current rating and low DC resistance is recommended. The inductance value can be calculated from the following formula:

$$L = \frac{V_{IN} \times (V_{OUT} - V_{IN})}{V_{OUT} \times \Delta i_L \times f_s}$$

Where  $\Delta i_{L}$  is the inductor current ripple. It is recommended the inductor current ripple to be around 30%~50% of the input current.

#### Setting the Input Capacitor

The input capacitor (C1) is required to maintain the DC input voltage. Ceramic capacitors with low ESR/ESL types are recommended. The input voltage ripple can be estimated by:

$$\Delta V_{IN} = \frac{V_{IN}}{8 \times f_s^2 \times L \times C_1} \times (1 - \frac{V_{IN}}{V_{OUT}})$$

Typically, a 10 $\mu$ F X7R ceramic capacitor is recommended.

#### Setting the Output Capacitor

The output current to the step-up converter is discontinuous, therefore a capacitor is essential to supply the AC current to the load. Use low ESR capacitors for the best performance. Ceramic capacitors with X7R dielectrics are highly recommended because of their low ESR and small temperature coefficient. The output voltage ripple can be estimated by:

$$\Delta V_{OUT} \ = \frac{V_{OUT}}{C_2 \times f_S \times R_L} \times (1 - \frac{V_{OUT}}{V_{OUT}})$$

Typically, a  $10\mu F$  X7R ceramic capacitor is recommended.

#### **RC Snubber Circuit**

When the chip is used in  $V_{OUT}$ =5V condition, a RC snubber should be added to protect the MOSFET from over voltage. The recommended parameters are R3=5.1 $\Omega$ , C5=1nF. The circuit can be seen in Figure 2.

Figure2—V<sub>OUT</sub>=5V Typical Application Circuit

#### **PCB** Layout

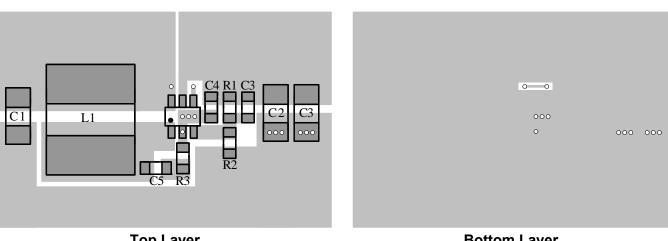

PCB layout is very important to achieve stable operation. Please follow these guidelines and take Figure 3 for references.

- 1) The output capacitor should be placed as close as possible to IC and forms a smallest loop with IC SW and GND pins. as C4 shown in figure2.

- 2) Adding RC snubber circuit from SW pin to GND pin to reduce the SW spike in 5V application.

- 3) Route SW away from sensitive analog areas such as FB.

Figure3—PCB Layout

# **PACKAGE INFORMATION**

TSOT23-6

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.